논문 2020-57-9-4

# NOR Flash를 위한 하프늄 옥사이드 기반 비휘발성 메모리 소자에서의 사파이어 기판을 통한 Self-heating Effect 및 Retention 개선

( Improvement of Self-heating Effect and Retention Characteristics in  $\text{HfO}_2$ -Based Nonvolatile Memory For NOR Flash By Utilizing Sapphire Substrate )

송 영 서\*, 김 현 우\*\*

( Young Suh Song<sup>①</sup> and Hyunwoo Kim )

## 요 약

본 논문에서는 NOR Flash를 위한 하프늄 옥사이드(Hafnium oxide,  $\text{HfO}_2$ ) 기반 비휘발성 메모리 소자를 설계하는데 있어, 기존의 SOI(Silicon On Insulator) 기반 TAHOS(TaN/ $\text{Al}_2\text{O}_3$ / $\text{HfO}_2$ / $\text{SiO}_2$ /Si) 구조를 대체할 SOS(Silicon On Sapphire) 기반 TAHOS 구조를 제안하였다. 사파이어(Sapphire,  $\text{Al}_2\text{O}_3$ ) 물질의 뛰어난 열전도도(Thermal conductivity)를 활용하여, TAHOS 구조가 최근 겪어온 자기가열효과(Self-heating Effect)와 보존성(Retention) 문제를 개선하고자 하였다. SOS 기반 TAHOS 소자의 경우 사파이어 물질이 효과적으로 열 방출구(Heat sink)로 작용하여 self-heating effect 문제가 개선이 되며, 이는 전하트 랙층 전자가 열에너지를 얻는 것을 억제하여 Retention 또한 개선되는 것을 알 수 있었다.

## Abstract

In this paper, in designing improved  $\text{HfO}_2$ (Hafnium oxide) based nonvolatile memory for NOR Flash application, SOS(Silicon On Sapphire) based TAHOS(TaN/ $\text{Al}_2\text{O}_3$ / $\text{HfO}_2$ / $\text{SiO}_2$ /Si) structure is proposed as substitutable candidate for replacing conventional SOI(Silicon On Insulator) based TAHOS structure. By utilizing the magnificent thermal conductivity of sapphire( $\text{Al}_2\text{O}_3$ ) materials, we tried to improve self-heating effect and retention issue that the TAHOS structure has suffered. In the case of proposed SOS based TAHOS structure, it has been demonstrated that self-heating effect can be significantly improved since the sapphire material effectively acts as a heat sink. Furthermore, it has been shown that this suppression of self-heating effect can suppresses the electrons in charge trap layer (CTL) from obtaining thermal energy, thereby retention characteristic can be improved.

**Keywords:** 노어 플래시, 자기가열효과, 보존성, 하프늄 옥사이드, 비휘발성 메모리

## I. 서 론

최근 빅데이터 시대의 도래와 함께<sup>[1~3]</sup> 5세대(Fifth-generation, 5G) 무선 네트워크 산업이 발달하면서<sup>[4, 5]</sup>

\*정회원, 육군사관학교(Korea Military Academy)

\*\*학생회원, 서울대학교 전기정보공학부(Dept. of Electrical and Computer Engineering, SNU)

①Corresponding Author(E-mail : sys1413@snu.ac.kr)

※ 본 논문은 육군사관학교 화랑대연구소의 2020년도 연구활동비 지원을 받아 연구되었음.

Received ; July 29, 2020      Revised ; September 6, 2020

Accepted ; September 6, 2020

높은 저장용량을 갖는 메모리 수요는 점점 증가해 왔다. 이에 따라, 21세기 이후 메모리 산업에서는 각 메모리 셀의 크기를 줄여 높은 집적도를 달성해 왔다<sup>[6]</sup>. 하지만 메모리 셀의 크기를 줄여서 집적도를 높이는 것은 메모리 소자에서 단위 면적당 자기가열효과(Self-heating Effect, SHE)를 불가피하게 증가시켜 왔다<sup>[7, 8]</sup>.

또한, 최근 들어 메모리 산업에서는 정보를 저장하는 전하 트랩층(Charge Trapping Layer, CTL) 물질로 기존의 실리콘 나이트라이드(Silicon nitride,  $\text{Si}_3\text{N}_4$ )를 대체하기 위해 하프늄 옥사이드(Hafnium oxide,  $\text{HfO}_2$ )

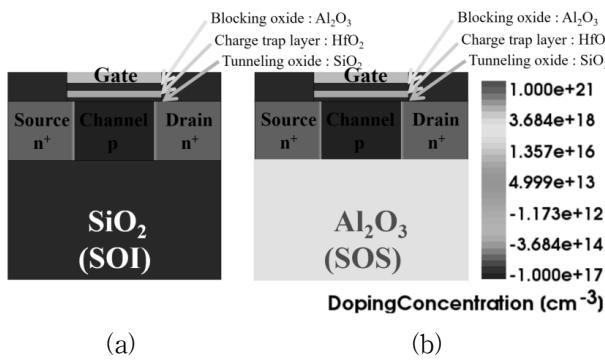

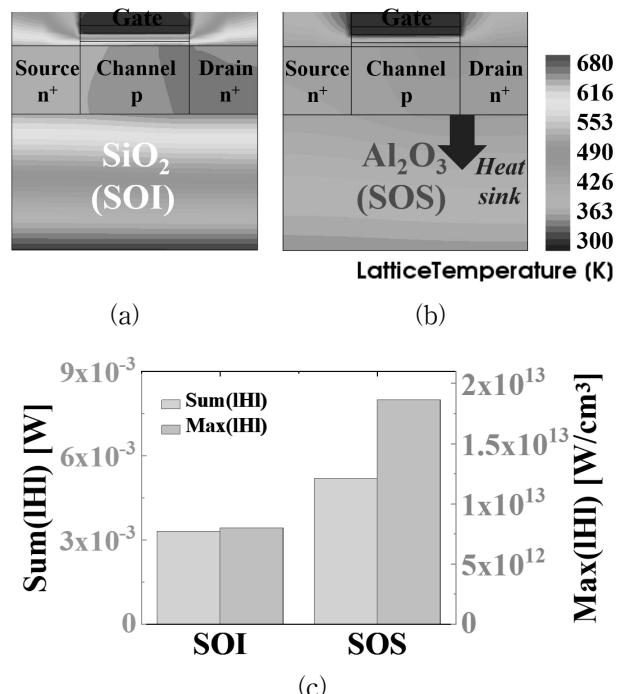

그림 1. (a) 기존의 SOI 기반 TAHOS 소자 구조와

(b) 제안한 SOS 기반 TAHOS 소자 구조

Fig. 1. (a) Conventional SOI based TAHOS structure and

(b) the proposed SOS based TAHOS structure.

표 1. 사용된 소자 파라미터들와 각각의 수치들

Table 1. Used device parameters and their corresponding values.

| Symbol              | Model Parameter                       | Value | Unit    |

|---------------------|---------------------------------------|-------|---------|

| $L_{gate}$          | Gate length                           | 80    | nm      |

| $T_{channel}$       | Channel thickness                     | 50    |         |

| $T_{BLK}$           | Blocking oxide thickness              | 6     |         |

| $T_{CTL}$           | CTL thickness                         | 6     |         |

| $T_{TNL}$           | Tunneling oxide thickness             | 3     |         |

| $T_{SOI}$           | SOI substrate thickness               | 300   |         |

| $T_{SOS}$           | SOS substrate thickness               | 300   |         |

| $\kappa_{HfO2}$     | HfO <sub>2</sub> thermal conductivity | 0.49  |         |

| $\kappa_{SiO2}$     | SiO <sub>2</sub> thermal conductivity | 1.4   |         |

| $\kappa_{Si}$       | Silicon thermal conductivity          | 7.5   | W/(m*K) |

| $\kappa_{Sapphire}$ | Sapphire thermal conductivity         | 29    |         |

물질을 많이 연구하고 있다<sup>[9, 10]</sup>. 그 이유는 하프늄 옥사이드의 경우 다음 2가지 이유에서 차세대 메모리 소자 물질로 적합하기 때문이다; 1) 전하트랩밀도(Charge Trap Density)가 기존의 실리콘 나이트라이드에 비해 4배로 훨씬 많은 정보를 저장할 수 있으며<sup>[11]</sup> 2) 유전율 또한 실리콘 나이트라이드 대비 약 3배로 더 낮은 전압에서 메모리의 읽기 및 쓰기 동작을 수행할 수 있다<sup>[12~17]</sup>.

하지만 이런 장점에도 불구하고, 하프늄 옥사이드 물질은 열전도도(Thermal conductivity)가 0.49 W/(m\*K)로, 실리콘 나이트라이드 30 W/(m\*K)에 비해 현저히

떨어진다<sup>[18, 19]</sup>. 따라서 하프늄 옥사이드 기반 비휘발성 메모리 소자의 경우 Self-heating Effect 문제가 크게 발생하며, 이렇게 높은 메모리 소자의 온도는 메모리 소자의 보존성(Retention) 문제로 이어진다<sup>[20]</sup>.

따라서, 이번 논문에서는 기존에 누설전류(Leakage current) 등을 줄이기 위하여 사용되어 왔던 일반적인 실리콘 산화막(Silicon dioxide, SiO<sub>2</sub>) 기반의 SOI(Silicon on insulator) 기판이 아닌 SOS(Silicon on sapphrie)를 사용함으로써 Self-heating Effect 및 Retention을 개선하고자 하였다. SOS 기판의 사파이어(Sapphire, Al<sub>2</sub>O<sub>3</sub>) 물질의 경우, 열 전도도가 29 W/(m\*K)로 SOI의 실리콘 산화막(Silicon dioxide, SiO<sub>2</sub>) 대비 20배 이상 높기 때문에 열을 잘 방출한다. 이러한 이점을 살리기 위해서 사파이어를 용용한 메모리 구조를 설계하였으며, 메모리 소자의 Self-heating Effect와 Retention을 개선해보고자 하였다.

## II. 본론

### 1. 소자 세부 정보 및 사용된 물리 모델

본 연구는 TAHOS(TaN/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/SiO<sub>2</sub>/Si) 소자 구조를 Synopsys Sentaurus Techonology Computer-Aided Design(TCAD) 시뮬레이터를 통해 분석하였다. 또한, 크게 2가지의 소자 구조를 사용하여 전기적 성질과 열역학적 성질을 비교분석(Comparative analysis)하였다. 그림 1(a)는 대조군으로 사용된 SOI 기반 TAHOS 소자를 나타내며, 그림 1(b)는 제안한 소자 구조인 SOS 기반 TAHOS 소자이다. 두 구조 모두 80 nm의 Gate Length (L<sub>gate</sub>)를 가지고 있으며, 채널 두께는 50 nm이다. 또한 소스/채널/드레인은 각각  $1 \times 10^{21}$  /  $1 \times 10^{17}$  /  $1 \times 10^{21}$  cm<sup>-3</sup>의 도핑농도를 갖고 있다. 정보를 저장하는 전하트랩층은 하프늄 옥사이드로 구성되어 있으며,  $1.2 \times 10^{20}$  cm<sup>-3</sup>의 전하트랩밀도를 갖는다. 소자 구조의 세부적인 정보는 표 1에서 나타내었다.

본 연구에서는 전기적 그리고 열역학적 분석을 위해 thermodynamic, Shockley-Read-Hall(SRH) Recombination, high field saturation, 그리고 fermi 모델이 사용되었다. 전자와 정공의 터널링 메커니즘으로는 Band-to-Band Tunneling(BTBT), Trap-Assisted-Tunneling(TAT), direct tunneling를 소자의 대기 전류(I<sub>off</sub>)와 구동 전류(I<sub>on</sub>)를 정확히 모델링하기 위해 사용했으며, 그리고 Fowler Nordheim(FN) tunneling을 메모리 소자의 프로그래밍 동작과 Retention 분석을 위하여 사용되었다.

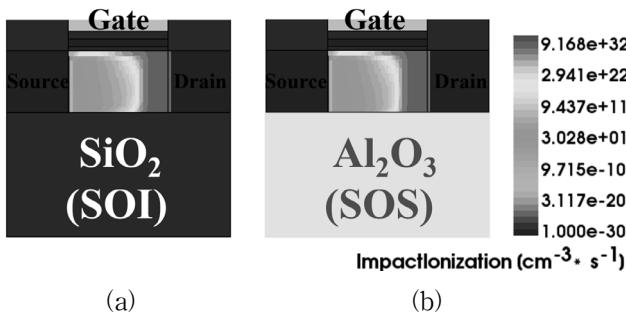

그림 2. (a) 기존의 SOI 기반 TAHOS 소자 구조에서의 프로그래밍 시 Impact Ionization (b) 제안한 SOS 기반 TAHOS 소자 구조에서의 프로그래밍 시 Impact Ionization

Fig. 2. Impact Ionization during programming at (a) conventional SOI based TAHOS structure and (b) the proposed SOS based TAHOS structure.

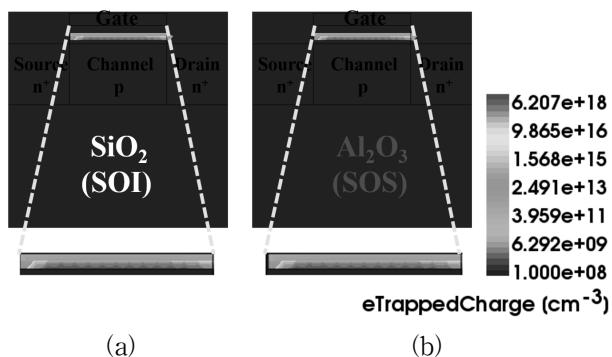

그림 3. (a) 기존의 SOI 기반 TAHOS 소자 구조에서의 프로그래밍 후 트랩된 전하량 (b) 제안한 SOS 기반 TAHOS 소자 구조에서의 프로그래밍 후 트랩된 전하량

Fig. 3. Amount of trapped electron charge after programming at (a) conventional SOI based TAHOS structure and (b) the proposed SOS based TAHOS structure.

## 2. 소자 구조에 따른 Self-heating Effect

소자를 프로그래밍하는데는 NOR Flash 메모리에서 주로 사용되는 Hot Carrier Injection(HCI) 방법을 사용하였다<sup>[19]</sup>. Impact ionization을 모델링하기 위해서, Mobility 모델(eHighFieldsat (GradQuasiFermi) / hHighFieldsat(CarrierTempDrive))을 사용하였다. 소자를 프로그래밍 하는데 있어서는, 게이트와 드레인에 각각 4, 6 V가 약 25 us동안 인가되었다. 그 결과 그림 2처럼 Impact ionization이 발생하며, Impact ionization으로 생긴 전자가 전하트랩층에 저장되는 것을 그림 3를 통해 알 수 있다.

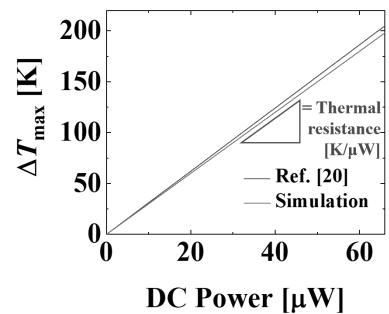

그림 4. 선행 연구의 실험 결과를 바탕으로 한 self-heating effect calibration 결과.

Fig. 4. Self-heating effect calibration results based on experiment results<sup>[20]</sup>.

그림 5. (a) 프로그래밍 직후 기존의 SOI 기반 TAHOS 소자 구조에서의 self-heating effect (b) 프로그래밍 직후 제안한 SOS 기반 TAHOS 소자 구조에서의 self-heating effect (c) Heat flux 비교

Fig. 5. Self-heating effect just after programming at (a) conventional SOI based TAHOS structure, (b) the proposed SOS based TAHOS structure, (c) heat flux comparison.

그림 4는 선행 연구를 바탕으로 한 self-heating effect calibration 결과를 나타낸다. Self-heating effect를 계산하기 위해서 Thermodynamic 모델을 사용하였으며, 또한 열 전도율, 열 전도 경로(Heat conductionpath), 그리고 열 경계 조건(Thermal boundary condition, 300K)를 각 열 경로(Heat path)에 적용함으로써 calibration을 진행하였다.

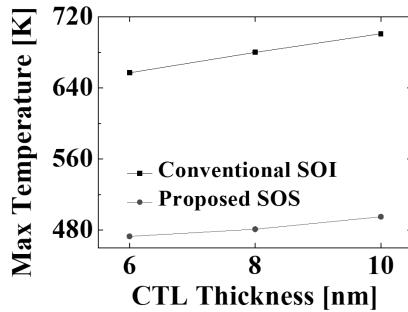

그림 6. CTL 두께 관련 프로그래밍 직후 기존 SOI 기반 TAHOS 소자와 제안한 SOS 기반 TAHOS 소자에서의 최대 온도

Fig. 6. Maximum temperature at conventional SOI based TAHOS structure and the proposed SOS based TAHOS structure with regard to CTL thickness.

진행하였다. 그 결과, 그림 4와 같이 시뮬레이션 결과가 잘 matching 되는 것을 알 수 있었다.

그림 5는 프로그래밍 직후에 소자에 생기는 Self-heating Effect를 나타낸다. 제안한 소자 구조의 SOS 기판의 경우 [그림 5(b)], 대조군인 SOI 구조 [그림 5(a)] 대비 열전도도가 20배기 때문에 훨씬 Self-heating Effect가 개선된 것을 알 수 있다. 구체적으로는, SOS 기판은 SOI 기판에 비해 열전도도가 20 배이기 때문에, 상당한 heat flux가 발생하며 [그림 5(c)] 그로 인해 최대온도가 474도로 열적으로 훨씬 안정된 것을 알 수 있다 [그림 5(b)]. 이러한 개선은 그림 6처럼 다양한 전하트랩층 두께에서도 또한 적용되는 것을 알 수 있다.

### 3. 소자 구조에 따른 Retention

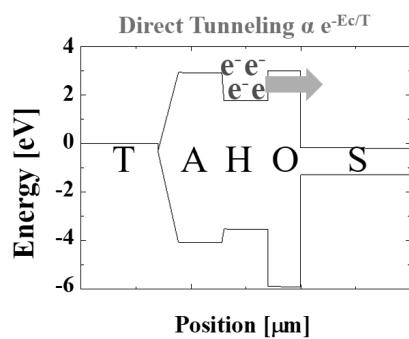

이러한 소자의 Self-heating Effect 차이는 소자의 Retention 차이로 연결된다<sup>[21]</sup>. 그림 7은 프로그래밍 후 100 second (Sec) 동안의 Retention을 나타낸다. 분석 구간을 프로그래밍 후 1 micro second에서 100 second로 잡은 이유는, 가열된 메모리 소자는 대개 100 second 이내에 온도가 원상태로 돌아오기 때문으로<sup>[22]</sup>, 프로그래밍 100 second 이후의 Retention은 소자의 Self-heating Effect에 의한 영향을 받았다고 결론 짓기 어렵기 때문이다.

기존의 소자에 비해 훨씬 Retention이 우수한 것을 알 수 있는데, 이는 에너지 밴드 다이어그램 [그림 8]을 통해 설명 가능하다. 기존의 SOI 기반 소자에 비해 제안한 SOS 기반 소자는 Self-heating Effect가 덜하기 때문에, 전하트랩층에 저장된 전자의 Direct Tunneling이 발생할 확률이 낮아지기 때문이다[그림 8]. 자세한 설명은 아래 수식을 통해 설명할 수 있다.

그림 7. 기존의 SOI 기반 TAHOS 소자와 제안한 SOS 기반 TAHOS 소자에서의 Retention 특성

Fig. 7. Retention characteristics at conventional SOI based TAHOS structure and the proposed SOS based TAHOS structure.

그림 8. TAHOS 구조의 에너지 밴드 다이어그램

Fig. 8. Energy band diagram with TAHOS structure.

$$I_{\text{Direct Tunneling}} \propto e^{-\frac{E_C}{T}} \quad (1)$$

유전체를 통과하면서 터널링이 일어나는 현상인 Direct Tunneling의 경우, 식 (1)에서도 알 수가 있듯이 온도가 높아지면 기하급수적으로 증가하는 것이 선행 연구를 통해서 밝혀졌다<sup>[23~25]</sup>. 온도와 Direct Tunneling과의 관계는 모델링 뿐만이 아니라<sup>[23]</sup>, 실제 반도체 소자를 통한 측정 데이터를 통해서도 많이 밝혀진 바가 있다<sup>[23, 24]</sup>.

따라서 제안한 SOS 기반 소자는 Self-heating Effect 측면에서 우수하며, 이는 Retention의 개선으로 연결되는 것을 알 수 있다.

### IV. 결론 및 후속 연구 제안

본 논문에서는 기존의 SOI 기반 TAHOS 소자를 대체할 메모리 소자로 SOS 기반 TAHOS 소자를 제안하

였다. SOS 기반 TAHOS 소자의 경우, 사파이어(Sapphire,  $Al_2O_3$ ) 물질의 뛰어난 열전도로부터 Self-heating Effect가 개선되며 결과적으로 Retention 또한 개선되는 것을 알 수 있었다. 이번 연구를 통해 차세대 메모리 소자인 하프늄 옥사이드 기반 메모리 소자가 몇 년 동안 겪어 왔던 Retention 문제와 본질적으로 갖고 있는 Self-heating 문제를 동시에 개선하였다.

본 논문의 핵심인  $Al_2O_3$ 의 높은 열 전도도를 활용하여 Retention을 개선하는 것을 더 발전시키면 NAND Flash에 적용할 수 있을 것으로 기대된다. 구체적으로는, 마카로니(Macaroni) 구조의 3D NAND Flash에서 절연층을  $Al_2O_3$ 을 활용하면 SHE도 개선되며, Retention을 포함한 소자의 신뢰성(Reliability) 또한 개선될 것으로 기대 된다.

## REFERENCES

- [1] S. Madden, "From Databases to Big Data," *IEEE Internet Computing*, Vol. 16, no. 3, pp. 4–6, May–June 2012.

- [2] T. Kim, et al., "Input-modulating adaptive neuron circuit employing asymmetric floating-gate MOSFET with two independent control gates," *Solid-State Electronics*, Vol. 163, Jan. 2020.

- [3] Y. S. Song, "Prediction of National Pension Exhaustion Time in Republic of Korea by Using Back propagation Algorithm," *Journal of the Institute of Electronics and Information Engineers*, Vol. 57, no. 7, July 2020.

- [4] A. Gupta and R. K. Jha, "A Survey of 5G Network: Architecture and Emerging Technologies," *IEEE Access*, Vol. 3, pp. 1206–1232, July 2015.

- [5] T. Kim, Y. S. Song and B. -G. Park, "Overflow Handling Integrate-and-Fire Silicon-on-Insulator Neuron Circuit Incorporating a Schmitt Trigger Implemented by Back-Gate Effect," *Journal of Nanoscience and Nanotechnology*, Vol. 19, no. 10, pp. 6183–6186, Oct. 2019.

- [6] H. Kim, S. Ahn, Y. G. Shin, K. Lee and E. Jung, "Evolution of NAND Flash Memory: From 2D to 3D as a Storage Market Leader," in Proc. of IEEE International Memory Workshop (IMW), Monterey, USA, pp. 1–4, May 2017.

- [7] E. Bury, et al., "Self-heating in FinFET and GAA-NW using Si, Ge and III/V channels," in Proc. of IEEE International Electron Devices Meeting (IEDM), San Francisco, USA, pp. 15.6.1–15.6.4, Dec. 2016.

- [8] S. Shin et al., "Direct Observation of Self-Heating in III - V Gate-All-Around Nanowire MOSFETs," *IEEE Transactions on Electron Devices*, Vol. 62, no. 11, pp. 3516–3523, Nov. 2015.

- [9] F. Driussi, S. Spiga, A. Lamperti, G. Congedo and A. Gambi, "Simulation Study of the Trapping Properties of HfO<sub>2</sub>-Based Charge-Trap Memory Cells," *IEEE Transactions on Electron Devices*, Vol. 61, no. 6, pp. 2056–2063, June 2014.

- [10] S. M. Amoroso, C. Monzio Compagnoni, A. Mauri, A. Maconi, A. S. Spinelli and A. L. Lacaita, "Semi-Analytical Model for the Transient Operation of Gate-All-Around Charge-Trap Memories," *IEEE Transactions on Electron Devices*, Vol. 58, no. 9, pp. 3116–3123, Sep. 2011.

- [11] Y. S. Song, et al., "Tunneling oxide engineering for improving retention in nonvolatile charge-trapping memory with TaN/ $Al_2O_3$ /HfO<sub>2</sub>/SiO<sub>2</sub>/ $Al_2O_3$ /SiO<sub>2</sub>/Si structure," *Japanese Journal of Applied Physics*, Vol. 59, no. 6, pp. 061006-1–061006-7, June 2020.

- [12] Y. Choi, et al., "Simulation of the effect of parasitic channel height on characteristics of stacked gate-all-around nanosheet FET," *Solid-State Electronics*, Vol. 164, pp. 107686, Feb. 2020.

- [13] J. Yu, et al., "Investigation of Ambipolar Current Suppression Using Dual Work Function Metal Gate in L-Shaped Tunnel Field Effect Transistor," in Proc. of IEIE Summer Conference, Jeju-do, Republic of Korea, pp. 52–53, June 2019.

- [14] Y. Kim, et al., "An Area Efficient Adaptive Neuron Circuit Exploiting Tunnel Field-Effect Transistor," in Proc. of IEIE Summer Conference, Jeju-do, Republic of Korea, pp. 71–73, June 2019.

- [15] Y. S. Song, et al., "Radius Scaling of Silicon-Based Nanowire Tunnel FET with Gate Dielectric Modulation," in Proc. of IEIE Fall Conference, Incheon, Republic of Korea, pp. 85–87, Nov. 2018. <http://www.dbpia.co.kr/Journal/articleDetail?nodeId=NO DE07624775>

- [16] T. Kim, K. Park, T. Jang, M. -H. Baek, Y. S. Song and B. -G. Park, "Input-modulating adaptive neuron circuit employing asymmetric floating-gate MOSFET with two independent control gates," *Solid-State Electronics*, Vol. 163, Jan. 2020.

- [17] J. H. Kim, et al., "Analysis of Current Variation with Work Function Variation in L-Shaped Tunnel-Field Effect Transistor," *Micromachines*, Vol. 11, no. 8, pp. 780–789, Aug. 2020.

- [18] Y. S. Song, S. Hwang, K. K. Min, T. Jang, Y. Choi, J. Yu, J. -H. Lee and B. -G. Park, "Electrical and Thermal Performances of Omega-Shaped-Gate Nanowire Field Effect Transistors for Low Power

- Operation," *Journal of Nanoscience and Nanotechnology*, Vol. 20, no. 7, pp. 4092–4096, July 2020.

- [19] H. Kim, et al., "Mitigation of Self-heating Effects in 3 nm Node Nanoplate-FET, *Journal of the Institute of Electronics and Information Engineers*," Vol. 57, no. 2, pp. 21–26, Feb. 2020.

- [20] I. Myeong, et al., "Analysis of Self Heating Effect in DC/AC Mode in Multi-Channel GAA-Field-Effect Transistor," Vol. 66, no. 11, pp. 4631–4637, Nov. 2019.

- [21] K. Wang, Z. Lun, W. Chen, X. Liu and G. Du, "Impact of self-heating effect on the retention of 3-D NAND flash memory," in *Proc. of IEEE 24th International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA)*, Chengdu, China, pp. 1–4, July 2017.

- [22] I. Fiorello, et al., "Rose-Inspired Micro-device with Variable Stiffness for Remotely Controlled Release of Objects in Robotics," *Proc. of Conference on Biomimetic and Biohybrid Systems*, Nara, Japan, pp. 122–133, July 2019.

- [23] A. Altland, D. Bagrets and A. Kamenev, "SYK non Fermi Liquid Correlations in Nanoscopic Quantum Transport," *Phys. Rev. Letter*, Vol. 123, Aug. 2019.

- [24] G. Darbandy, et al., "Temperature dependent compact modeling of gate tunneling leakage current in double gate MOSFETs," *Solid-State Electronics*, Vol. 81, pp. 124–129, March 2013.

- [25] C. -C. Lin and J. -G. Hwu, "Performance enhancement of metal-oxide-semiconductor tunneling temperature sensors with nanoscale oxides by employing ultrathin Al<sub>2</sub>O<sub>3</sub> high-k dielectrics," *Nanoscale*, Vol. 5, pp. 8090–8097, July 2013.

---

### 저자 소개

---

송 영 서(정희원)

2018년 서울대학교 전기정보공학부 학사 졸업.

2020년 서울대학교 전기정보공학부 석사과정(석박통합)

2020년 ~ 현재 서울대학교 전기정보공학부 박사과정

(석박통합)

2020년 6월 ~ 현재 육군사관학교 이학처 컴퓨터과학과 교수부 교수사관

<주관심분야: NAND Flash, NOR Flash, AI 반도체, Self-heating Effect, 반도체 소자 신뢰성>

김 현 우(학생회원)

2018년 광주과학기술원 전기전자 컴퓨터공학과 학사 졸업.

2020년 서울대학교 전기정보공학부 석사 졸업

<주관심분야: 반도체 소자 Self-heating Effect>