# Material-Device Simulations of High-Frequency Performances of *n*-type MOSFET with GeSn Channel

Soomin Kim<sup>1</sup>, Md. Hasan Raza Ansari<sup>2</sup>, and Seongjae Cho<sup>1,\*</sup>

**Abstract:** Recently, GeSn has been identified as a promising candidate for group-IV-driven electronic and photonic devices owing to its high carrier mobility and indirect-to-direct bandgap transition property. In this work, a comprehensive study of primary material characteristics, including electron affinity, bandgap energies at local minimum valleys, and effective density of states (DOS) of the GeSn alloy, has been conducted as a function of Sn fraction and in-volume stress. As the Sn fraction increases, leading to the transition from an indirect-to-direct bandgap, the electron affinity rises sharply, while the energy bandgap and the effective DOS decrease. Based on these material parameters, an *n*-type metal-oxide-semiconductor field-effect transistor has been designed and optimized in terms of DC parameters and high-frequency performance as a function of Sn fraction and the corresponding in-volume biaxial stress in the channel region. As tensile stress or Sn fraction increases, both the on-state ( $I_{on}$ ) and off-state currents ( $I_{off}$ ) rise due to a narrowed bandgap energy, while the subthreshold swing ( $S$ ) value also degrades. In contrast, compressive strain reduces  $I_{off}$ . Finally, the incorporation of GeSn channel is reported to be advantageous for high-speed operation.

**Index terms:** GeSn, group IV material, indirect-to-direct bandgap transition, in-volume biaxial strain, high-frequency performance

## I. INTRODUCTION

Given the scaling limits of conventional Si CMOS technology, functional materials with high carrier mobilities are increasingly being introduced. Ge, in particular, has garnered significant attention due to its high compatibility with Si and superior carrier mobility compared to Si [1-4]. Incorporating Sn atoms into Ge creates the notable alloy,  $Ge_{1-x}Sn_x$ , which has the potential to drive the next generation of both electronic and photonic devices with high

carrier mobility modulation and wide bandgap tunability [5-8]. This tunability not only allows control over the electrical bandgap magnitude but also facilitates the transition to a direct-bandgap material, a property not typically associated with conventional group-IV materials such as Si and Ge [9-12]. Consequently, Sn incorporation enhances the electrical and photonic properties of  $Ge_{1-x}Sn_x$ , making it suitable for low-power, high-speed electronic and photonic devices [13-17]. Due to the excellent properties of GeSn, studies on GeSn layer growth are also being actively conducted [18-21]. To achieve more accurate simulation results than previous studies, this work effectively couples the Perdew-Burke-Ernzerhof (PBE) and modified Becke-Johnson (mBJ) potential models for solids to characterize  $Ge_{1-x}Sn_x$ . A comprehensive analysis of material parameters was performed as a function of Sn fraction and in-volume biaxial strain. The latter part of this paper presents a systematic approach to device simulation (Silvaco ATLAS 2D with Deckbuild interface), applying the material parameters obtained from atomic-level simulations (Quantum Espresso). The study examines how

Manuscript received Sep. 8, 2024; revised Jan. 5, 2025; accepted Jan. 5, 2025

<sup>1</sup>Department of Electronic and Electrical Engineering, Ewha Womans University, Seoul 03760, Republic of Korea

<sup>2</sup>Computer, Electrical and Mathematical Science and Engineering Division (CEMSE), King Abdullah University of Science and Technology (KAUST), Thuwal 23955, Saudi Arabia

E-mail : felixcho@ewha.ac.kr

This manuscript has been prepared with an extension of the contents presented at 2024 Asia-Pacific Workshop on Advanced Semiconductor Devices (AWAD 2024) for the special issue of JSTS.

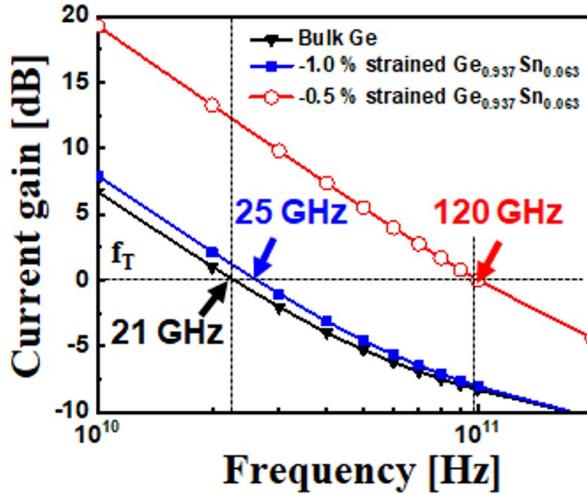

primary DC parameters, such as  $I_{on}$  and  $S$ , and high-frequency performance depend on Sn fraction and in-volume biaxial stress. Notably, the cut-off frequency ( $f_T$ ) does not exhibit a monotonic dependence on the magnitude of tensile strain in GeSn but instead shows a local maximum. The compressive strain increased  $f_T$ , reaching a maximum of 120 GHz at 0.5% strain.

## II. FIRST-PRINCIPLE SIMULATION STRATEGY

Full-potential and all-electron schemes with relativistic effects were considered in the first-principle simulation to achieve higher accuracy and credibility. A two-atom unit cell for the base structure was used to construct the supercell (SC) shown in Fig. 1. Sn atoms were then incorporated into the Ge SC to represent the alloy with a targeted Sn fraction. Volume optimization was performed using the PBE model for solids, ensuring minimum energy and zero pressure. The Sn fraction was controlled from 0% to 12.5%, confirming bandgap modulation, specifically the indirect-to-direct bandgap transition. Under these conditions, in-volume pressure was applied to the SCs as in-volume biaxial strain, varying the lattice constant from -2% (compressive strain) to +2% (tensile strain). Although this situation can be virtually manipulated, it can be realized by applying external stresses from materials with intentionally deposited thermal expansion coefficients during process integration. By varying the Sn fraction and in-volume biaxial strain, 15 distinct SC models were constructed, and the mBJ potential models were applied to obtain more realistic energy bandgap values at non-zero temperatures.

## III. RESULTS AND DISCUSSION

### 1. Material Simulation Results

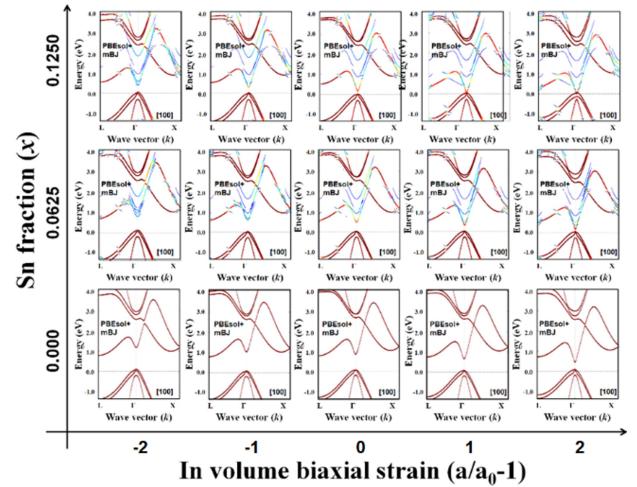

Fig. 2 shows a total of 15 E- $k$  band diagrams as a function of Sn fraction  $x$  and degrees of stress directions. The

Fig. 1. 16-atom Ge supercell comprising 2-atom unit cells used for *ab initio* calculations.

Fig. 2. E- $k$  diagram of  $\text{Ge}_{1-x}\text{Sn}_x$  as a function of Sn fraction  $x$  and in volume biaxial strain.

(a)

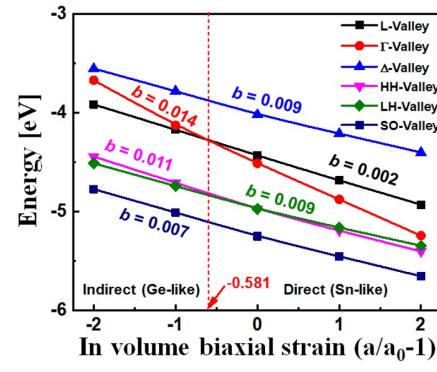

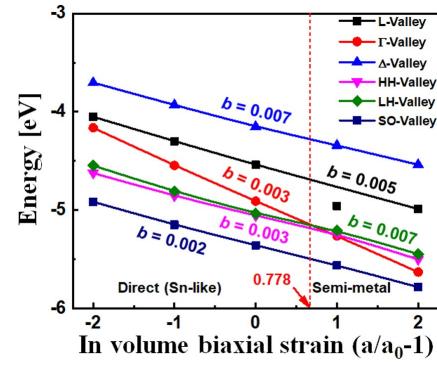

Fig. 3. Energy levels and bandgap transition as a function of the in-volume strain (a)  $\text{Ge}_{0.937}\text{Sn}_{0.063}$  and (b)  $\text{Ge}_{0.875}\text{Sn}_{0.125}$ .

Sn fraction increases along the vertical axis from 0.000 to 0.1250, while the stress varies along the horizontal axis from -2% to +2%. The color and point size represent the Bloch spectral weights, which are determined by both the degeneracy of the allowed quantum states and the cumulative effects of the corresponding Bloch characteristics

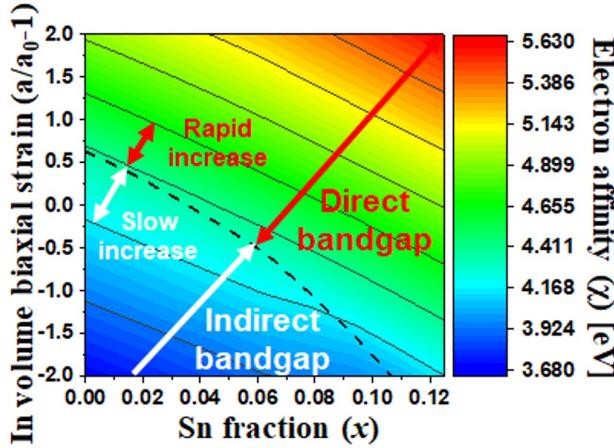

**Fig. 4.** Electron affinity of  $\text{Ge}_{1-x}\text{Sn}_x$  as a function of in-volume biaxial strain and Sn fraction.

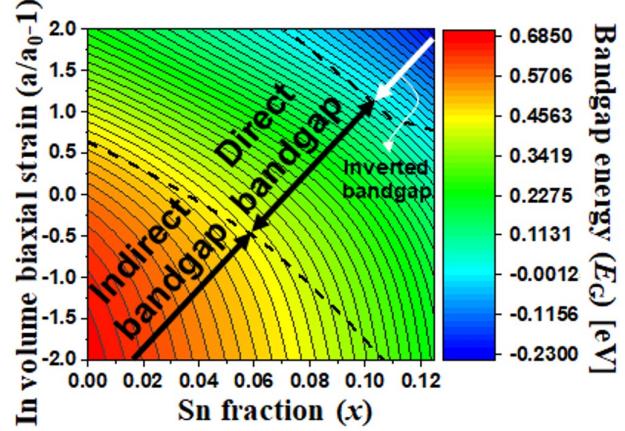

on the electron potential energy. Fig. 3 shows the energy levels of  $\text{Ge}_{0.937}\text{Sn}_{0.063}$  and  $\text{Ge}_{0.875}\text{Sn}_{0.125}$  at the L ( $E_L$ ),  $\Gamma$  ( $E_\Gamma$ ),  $\Delta$  ( $E_\Delta$ ) valleys; the heavy-hole and light-hole bands, along with the spin-orbit band, are also depicted. As the Sn fraction and external tensile strain increase, the bandgap energy becomes narrow. The indirect-to-direct bandgap transition occurred at approximately 0.581% compressive strain for  $\text{Ge}_{0.937}\text{Sn}_{0.063}$ , as shown in Fig. 3(a), and the direct-to-indirect bandgap transition occurred at approximately 0.778% tensile strain for  $\text{Ge}_{0.875}\text{Sn}_{0.125}$ , as shown in Fig. 3(b). The energy bandgap in the  $\Gamma$  valley decreases more rapidly compared to those in the L and  $\Delta$  valleys, leading to the indirect-to-direct bandgap transition. Even a small in-volume tensile strain, as small as 1%, induced a bandgap transition in  $\text{Ge}_{0.875}\text{Sn}_{0.125}$ . The electron affinity rapidly increases after the transition to a direct bandgap, as the  $\Gamma$  valley lowers faster than the L valley, as shown in Fig. 4. With an increase in Sn fraction, the bandgap energy and effective DOS values decrease sharply, as shown in Fig. 5. All extracted and calculated parameters representing the material characteristics at various Sn fractions and strain conditions were then fed into the device simulations for the design of the GeSn *n*-type metal-oxide-semiconductor field-effect transistor (NMOFSET) design.

## 2. Device Simulation Results

As recent researches have demonstrated, studies on the design and fabrication of GeSn-based devices are increasingly important, emphasizing the importance of utilizing the excellent properties of GeSn for various electronic device applications [22-25]. To achieve this, the growth

**Fig. 5.** Bandgap energy of  $\text{Ge}_{1-x}\text{Sn}_x$  as a function of in-volume biaxial strain and Sn fraction.

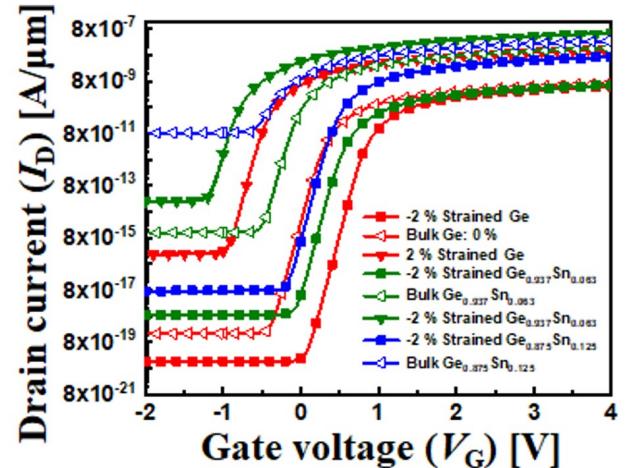

**Fig. 6.** Transfer curves of  $\text{Ge}_{1-x}\text{Sn}_x$  NMOSFETs at various Sn fractions under in-volume biaxial strain.

of high-quality single-crystalline GeSn on silicon platforms is crucial, as it ensures compatibility with existing Si-based technologies and enables practical device fabrication [26-29]. Most previous studies have focused on the application of  $\text{Ge}_{1-x}\text{Sn}_x$  to *p*-type MOSFETs, which typically exhibit a lower off-state current ( $I_{\text{off}}$ ) compared to NMOSFETs. However, this study controls the leakage current of the GeSn NMOSFET device through adjustments in Ge fraction and in-volume biaxial strain. The channel length of the GeSn NMOSFET is 800 nm, with Si and in-volume biaxial strained  $\text{Ge}_{1-x}\text{Sn}_x$  serving as the substrate and channel, respectively. Device simulations were conducted on 81 device structures under various conditions to ensure comprehensive analysis through a material-and-device cooperative design. Fig. 6 shows the transfer curves of  $\text{Ge}_{1-x}\text{Sn}_x$  NMOSFETs at various

**Fig. 7.** High-frequency performance as a function of Sn fraction and compressive strain, specifically at a Sn fraction of 6.3%.

Sn fractions and under in-volume biaxial stress. With increasing Sn fraction and tensile stress, both  $I_{on}$  and  $I_{off}$  increased due to bandgap narrowing and enhanced carrier mobility. Compressive strain effectively reduced  $I_{off}$ , demonstrating that an optimization can be achieved to balance  $I_{on}$  and  $I_{off}$ . In the case of tensile strain, the  $I_{on}/I_{off}$  maintains a high value of about  $10^8$ , and with compressive strain, it reaches approximately  $10^{10}$ , demonstrating superior on/off characteristics. Notably, compressive strain is suitable for implementing low-power devices by effectively reducing  $I_{off}$  while maintaining an appropriate level of  $I_{on}$ . However, increasing either tensile stress or Sn fraction led to a degradation in the subthreshold swing (S). Finally, Fig. 7 presents the high-frequency performance, including current gain and  $f_T$ , as a function of compressive strain in  $\text{Ge}_{0.937}\text{Sn}_{0.063}$ . A compressive strain of 0.5% in  $\text{Ge}_{0.937}\text{Sn}_{0.063}$  yielded an  $f_T$  of 120 GHz, significantly higher than the 21 GHz for MOSFETs with bulk Ge channels and the 25 GHz for 1.0% tensile-strained  $\text{Ge}_{0.937}\text{Sn}_{0.063}$  channels.

#### IV. CONCLUSION

In this work, a systematic study of  $\text{Ge}_{1-x}\text{Sn}_x$  was conducted using a bottom-up approach, linking material parameters and device design for greater credibility. The wide-range bandgap energy tunability and the indirect-to-direct bandgap transition of  $\text{Ge}_{1-x}\text{Sn}_x$  highlight its potential to address the current limitations of CMOS technology. Incorporating  $\text{Ge}_{1-x}\text{Sn}_x$  into the channel enhanced

high-speed performance and suppressed off-state leakage, given an appropriate Sn fraction and stress, as concluded through material-device co-design.

#### ACKNOWLEDGMENTS

This work was supported by the research projects of the National Research Foundation of Korea (NRF) funded by the Korean Ministry of Science and ICT (MSIT) under grants 2021M3H4A6A01048300 and RS-2023-00258527.

#### REFERENCES

- [1] M. Saito, K. Moto, T. Nishida, T. Suemasu, and K. Toko, "High-electron-mobility ( $370 \text{ cm}^2/\text{Vs}$ ) polycrystalline Ge on an insulator formed by As-doped solid-phase crystallization," *Scientific Reports*, vol. 9, no. 16558, pp. 1-6, Nov. 2019.

- [2] S. Cho, K. R. Kim, B.-G. Park, and I. M. Kang, "RF Performance and Small-Signal Parameter Extraction of Junctionless Silicon Nanowire MOSFETs," *IEEE Transactions on Electron Devices*, vol. 58, no. 5, pp. 1388-1396, May 2011.

- [3] S. Cho, S. Cheung, Y. H. Jung, S.-K. Kang, D. H. Lee, and B.-G. Park, "Ge-on-Si Photodetector with Enhanced Optical Responsivity by Advanced Metallization Geometry," *Journal of Semiconductor Technology and Science*, vol. 20, no. 4, pp. 366-371, Aug. 2020.

- [4] D. Kuzum, T. Krishnamohan, A. Nainani, Y. Sun, P. A. Pianetta, and H.-S. P. Wong, "High-Mobility Ge N-MOSFETs and Mobility Degradation Mechanisms," *IEEE Transactions on Electron Devices*, vol. 58, no. 1, pp. 59-66, Jan. 2011.

- [5] S. Ghosh, R. Bansal, G. Sun, R. A. Soref, H.-H. Chang, and G.-E. Chang, "Design and Optimization of GeSn Waveguide Photodetectors for 2- $\mu\text{m}$  Band Silicon Photonics," *Sensors*, vol. 22, no. 11, pp. 1-20, May 2022.

- [6] Z. Kong, G. Wang, R. Liang, J. Su, M. Xun, Y. Miao, S. Gu, J. Li, K. Cao, H. Lin, B. Li, Y. Ren, J. Li, J. Xu, and H. H. Radamson, "Growth and Strain Modulation of GeSn Alloys for Photonic and Electronic Applications," *Nanomaterials*, vol. 12, no. 6, pp. 1-15, Mar. 2022.

- [7] J. Lee, I. H. Cho, D. Seo, S. Cho, and B.-G. Park, "Characterization of GeSn deposited on Si by low-temperature sputter epitaxy," *Journal of Semiconductor Technology and Science*, vol. 16, no. 6, pp. 854-859, Dec. 2016.

- [8] M. A. Nawwar, M. S. A. Ghazala, L. N. S. El-Deen, and A. E. B. Kashyout, "Impact of strain engineering and Sn

content on GeSn heterostructured nanomaterials for nanoelectronics and photonic devices," *RSC Advances*, vol. 12, no. 38, pp. 24518-24554, Aug. 2022.

[9] S. A. Ghetmiri, W. Du, J. Margetis, A. Mosleh, L. Cousar, B. R. Conley, L. Domulevicz, A. Nazzal, G. Sun, R. A. Soref, J. Tolle, B. Li, H. A. Naseem, and S.-Q. Yu, "Direct-bandgap GeSn grown on silicon with 2230 nm photoluminescence," *Applied Physics Letters*, vol. 105, no. 15, pp. 151109-1-151109-5, Oct. 2014.

[10] P. C. Grant, J. Margetis, W. Du, Y. Zhou, W. Dou, G. Abernathy, A. Kuchuk, B. Li, J. Tolle, and J. Liu, "Study of direct bandgap type-I GeSn/GeSn double quantum well with improved carrier confinement," *Nanotechnology*, vol. 29, no. 46, pp. 1-9, Sep. 2018.

[11] J. Menéndez, P. M. Wallace, C. Xu, C. L. Senaratne, J. D. Gallagher, and J. Kouvettakis, "Materials physics of GeSn-based semiconductor lasers," *Materials Today: Proceedings*, vol. 14, no. 1, pp. 38-42, May 2019.

[12] P. Parrek and M. K. Das, "Theoretical analysis of direct transition in SiGeSn/GeSn strain balanced QWIP," *Optical and Quantum Electronics*, vol. 48, no. 228, pp. 1-11, Mar. 2016.

[13] S. Cho, R. Chen, S. Koo, G. Shambat, H. Lin, N. Park, J. Vuckovic, T. I. Kamins, B.-G. Park, and J. S. Harris, Jr., "Fabrication and analysis of epitaxially grown  $Ge_{1-x}Sn_x$  microdisk resonator with 20-nm free spectral range," *IEEE Photonics Technology Letters*, vol. 23, no. 20, pp. 1535-1537, Oct. 2011.

[14] J. S. Harris, H. Lin, R. Chen, Y. Huo, E. Fei, S. Cho, and T. Kamins, "MBE growth of GeSn and SiGeSn heterojunction for photonic devices," *ECS Transactions*, vol. 50, no. 9, 601-605, Oct. 2012.

[15] M. R. M. Atalla, S. Assali, S. Koelling, A. Attiaoui, and O. Moutanabbir, "High-bandwidth extended-SWIR GeSn photodetectors on silicon achieving ultrafast broadband spectroscopic response," *ACS Photonics*, vol. 9, no. 4, pp. 1425-1433, Mar. 2022.

[16] S. Xu, W. Wang, Y.-C. Huang, Y. Dong, S. Masudy-Panah, H. Wang, X. Gong, and Y.-C. Yeo, "High-speed photo-detection at two-micron-wavelength: technology enablement by GeSn/Ge multiple-quantum-well photodiode on 300 mm Si substrate," *Optics Express*, vol. 27, no. 4, pp. 5798-5813, Feb. 2019.

[17] N. Wang, C. Xue, F. Wan, Y. Zhao, G. Xu, Z. Liu, J. Zheng, Y. Zuo, B. Cheng, and Q. Wang, "High-Performance GeSn Photodetector Covering All Telecommunication Bands," *IEEE Photonics Journal*, vol. 13, no. 2, Apr. 2021.

[18] G. G. Jernigan, N. A. Mahadik, M. E. Twigg, E. M. Jackson, and J. A. Nolde, "SiGeSn buffer layer for the growth of GeSn films," *Journal of Applied Physics*, vol. 134, no. 2, pp. 025305-1-025305-7, Mar. 2023.

[19] H. Cai, K. Qian, Y. An, G. Lin, S. Wu, H. Ding, W. Huang, S. Chen, J. Wang, and C. Li, "Thickness-dependent behavior of strain relaxation and Sn segregation of GeSn epilayer during rapid thermal annealing," *Journal of Alloys and Compounds*, vol. 904, pp. 164068-1-164068-9, Jan. 2022.

[20] J. Margetis, A. Mosleh, S. A. Ghetmiri, S. Al-Kabi, W. Dou, W. Du, N. Bhargava, S. Q. Yu, H. Profijt, D. Kohen, R. Loo, A. Vohra, and J. Tolle, "Fundamentals of  $Ge_{1-x}Sn_x$  and  $Si_{y}Ge_{1-x-y}Sn_x$  RPCVD epitaxy," *Materials Science in Semiconductor Processing*, vol. 70, pp. 38-43, Nov. 2017.

[21] S. Dev, K. R. Khiangte, and S. Lodha, "Wafer-scale monocrystalline GeSn alloy on Ge by sputtering and solid phase epitaxy," *Journal of Physics D: Applied Physics*, vol. 53, no. 21, pp. 1-6, Mar. 2020.

[22] D. Lei, K. H. Lee, Y.-C. Huang, W. Wang, S. Masudy-Panah, S. Yadav, A. Kumar, Y. Dong, Y. Kang, S. Xu, Y. Wu, C. S. Tan, X. Gong, and Y.-C. Yeo, "Germanium-tin (GeSn) P-channel fin field-effect transistor fabricated on a novel GeSn-on-insulator substrate," *IEEE Transactions on Electron Devices*, vol. 65, no. 9, pp. 3754-3761, Sep. 2018.

[23] W. Wang, D. Lei, Y.-C. Huang, K. H. Lee, W.-K. Loke, Y. Dong, S. Xu, C. S. Tan, H. Wang, S.-F. Yoon, X. Gong, and Y.-C. Yeo, "High-performance GeSn photodetector and fin field-effect transistor (FinFET) on an advanced GeSn-on-insulator platform," *Optics Express*, vol. 26, no. 8, pp. 10305-10314, Apr. 2018.

[24] M. Liu, D. Yang, A. Shkurmanov, J. H. Bae, V. Schlykow, J.-M. Hartmann, Z. Ikonic, F. Baerwolf, I. Costina, A. Mai, J. Knoch, D. Grützmacher, D. Buca, and Q.-T. Zhao, "Epitaxial GeSn/Ge Vertical Nanowires for p-Type Field-Effect Transistors with Enhanced Performance," *ACS Applied Nano Materials*, vol. 4, no. 1, pp. 94-101, Dec. 2021.

[25] Y. Junk, M. Liu, M. Frauenrath, J.-M. Hartmann, D. Grützmacher, D. Buca, and Q.-T. Zhao, "Vertical GeSn/Ge heterostructure gate-all-around nanowire p-MOSFETs," *ECS Transactions*, vol. 108, no. 5, pp. 83-91, Jul. 2022.

[26] J. Lee, I. H. Cho, D. Seo, S. Cho, and B.-G. Park, "Catalysis and Characterization of GeSn Deposited on Si with Ge Buffer Layer by Low-temperature Sputter Epitaxy," *Journal of Semiconductor Technology and Science*, vol. 16, no. 6, pp. 854-859, Dec. 2016.

[27] W. Dou, B. Alharthi, P. C. Grant, J. M. Grant, A. Mosleh, H. Tran, W. Du, M. Mortazavi, B. Li, H. Naseem, and S.-Q. Yu, "Crystalline GeSn growth by plasma enhanced chemical vapor deposition," *Optical Materials Express*, vol. 8, no. 10, pp. 3220-3229, Oct. 2018.

[28] Y. Miao, G. Wang, Z. Kong, B. Xu, X. Zhao, X. Luo, H. Lin, Y. Dong, B. Lu, L. Dong, J. Zhou, J. Liu, and H. H. Radamson, "Review of Si-based GeSn CVD growth and

optoelectronic applications," *Nanomaterials*, vol. 11, no. 10, pp. 2556-1-2556-43, Sep. 2021.

[29] R. R. Lieten, C. Fleischmann, S. Peters, N. M. Santos, L. M. Amorim, Y. Shimura, N. Uchida, T. Maeda, S. Nikitenko, T. Conard, J.-P. Locquet, K. Temst, and A. Vantomme, "Structural and optical properties of amorphous and crystalline GeSn layers on Si," *ECS Journal of Solid State Science and Technology*, vol. 3, no. 12, pp. P403-P408, Oct. 2014.

**Soomin Kim** received the B.S. degree in electronic and electrical engineering from Ewha Womans University, Seoul, Korea, in 2023. She is currently pursuing an M.S. degree at Ewha Womans University. Her current research interests include novel semiconductor logic and memory devices in the nanoscale region, low-power synaptic devices and circuits, and scalable solid-state power source for CMOS integration. She is a Student Member of the Institute of Electronics and Information Engineers (IEIE).

**Hasan Ansari** received the M.Tech. degree in nanotechnology from the Vellore Institute of Technology (VIT), Vellore, India, in 2016, and a Ph.D. degree in electrical engineering from the Indian Institute of Technology (IIT), Indore, India, in 2019. After his Ph.D., he worked as a Postdoctoral Fellow at Gachon University, South Korea, from 2019 to 2021. Currently, he is working as a Postdoctoral Research Fellow in the Computer, Electrical and Mathematical Sciences and Engineering (CEMSE) Division at King Abdullah University of Science and Technology (KAUST). He is mainly interested in advanced logic, charge-trapping memory, emerging non-volatile memories, neuromorphic circuits, and in-memory and in-sensor computing.

**Seongjae Cho** received his B.S. and Ph.D. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 2004 and 2010, respectively. He worked as an Exchange Researcher at the National Institute of Advanced Industrial Science and Technology (AIST), Tsukuba, Japan, in 2009. He worked as a Postdoctoral Researcher at Seoul National University in 2010 and at Stanford University, Palo Alto, CA, from 2010 to 2013. Also, he worked as a faculty member at the Department of Electronic Engineering, Gachon University, from 2013 to 2023. He is currently working as an Associate Professor at the Division of Convergence Electronic and Semiconductor Engineering, Ewha Womans University, Seoul, Korea from 2023. His current interests include emerging memory devices, advanced nanoscale CMOS devices, optical interconnect devices, and novel devices for future computing. He is a Life Member of IEIE.